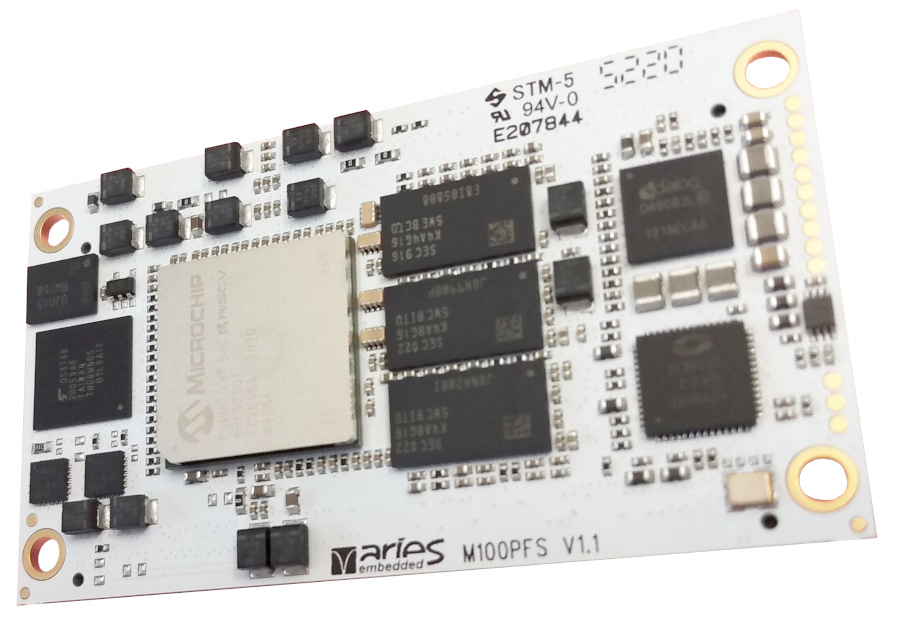

Product information "M100PFS-025A0A0E-1"

The M100PFS is based on the PolarFire SoC FPGA architecture by Microchip and combines high-performance 64-bit RISC-V cores with outstanding FPGA technology. The platform integrates a hardened real-time, Linux capable, RISC-V-based MPU subsystem on the mid-range PolarFire FPGA family, bringing low power consumption, thermal efficiency and defence grade security to embedded systems.

The RISC-V CPU micro-architecture implementation is a simple 5 stage, single issue, in-order pipeline that doesn’t suffer from the Meltdown and Spectre exploits found in common out-of-order machines. All five CPU cores are coherent with the memory subsystem allowing a versatile mix of deterministic real time systems and Linux in a single multi-core CPU cluster.

Order Code

- MPFS025T PolarFire SoC FPGA

- 23 KLEs

- 68 Math Blocks (18x18 MACC)

- 4x 12.7 Gbps SERDES lanes

- 2x PCIe Gen2 end points/root points

- Total User I/O: MSS-IO / HSIO / GPIO / XCVRs: 108 / 60 / 48 / 4

- 1GB DDR4 SDRAM dedicated to the HMS

- No DDR4 SDRAM dedicated to the FPGA

- No SPI NOR Flash

- 4 GB eMMC

- size 74mm x 42mm

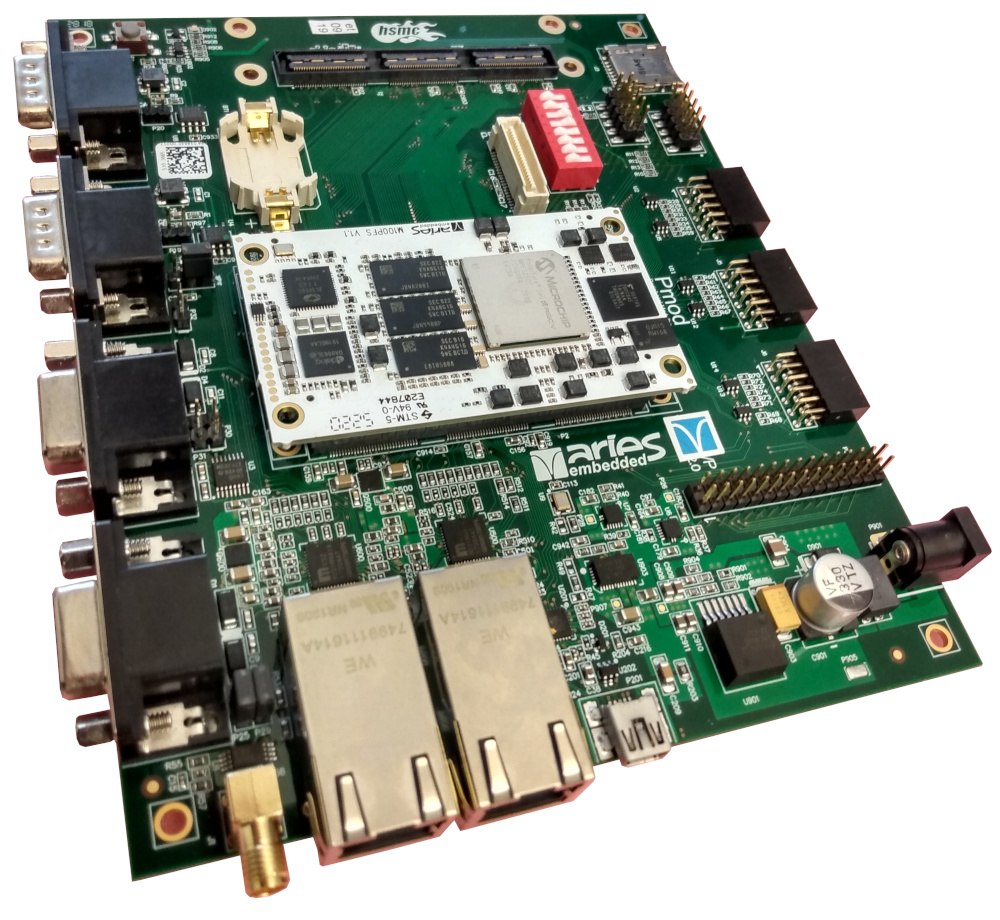

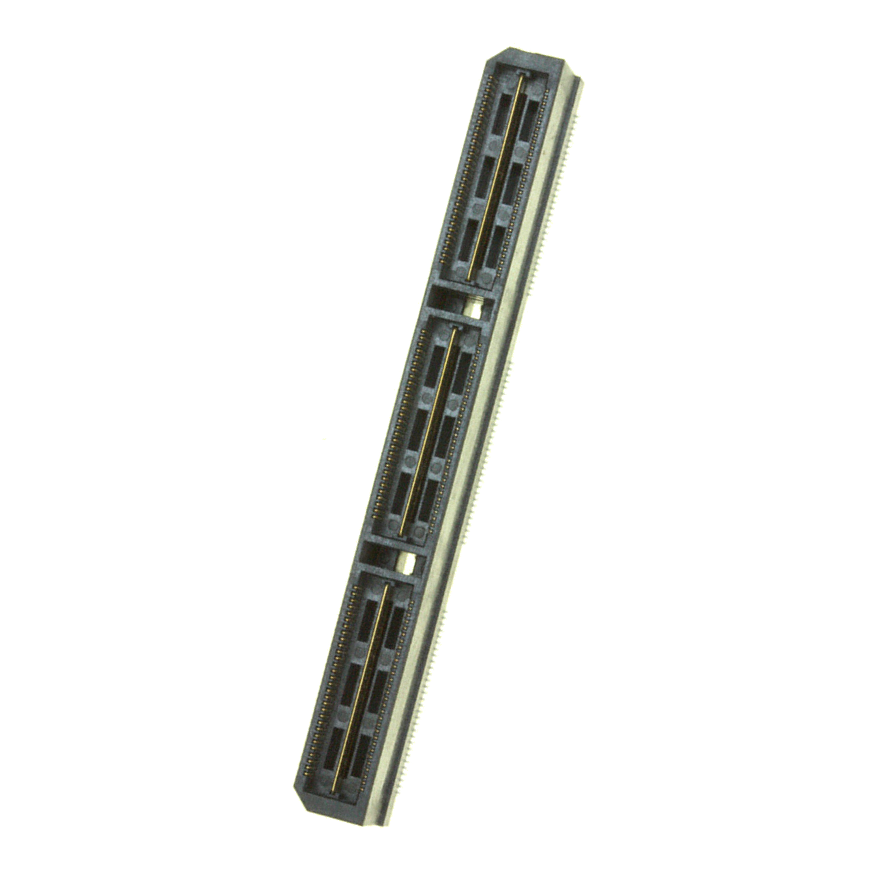

- 2 x Samtec QSH-090-01-F-D-A board-to-board interconnect

- 0°C...+70°C

Contact ARIES Embedded for Special Features and early Access